|

|

|

|

Main Features |

|

- Supports high-speed JTAG programming of a single Atmel AVR microcontroller connected via the JTAG interface

-

Supports high-speed JTAG programming of multiple Atmel AVR microcontrollers which are connected as part of a 'JTAG Chain' (JTAG daisy-chain mode).

-

Fast programming speeds via JTAG (3 - 4 times faster than SPI method)

-

Simple 4-wire JTAG Interface to microcontroller

-

Same JTAG Interface as Atmel JTAG ICE MK2 Debugger

-

User-selectable JTAG frequency

-

Supports JTAG Chain Validation

-

Supports checking of the 'JTAG ID' of both AVR and any generic JTAG devices eg. CPLD's

-

Supports automatic checking of 'Silicon Revision' of target JTAG device

|

|

Advantages of JTAG Programming |

|

- The JTAG algorithm is approximately 3-4 times faster at programming compared to the SPI algorithm.

-

The programming time using JTAG for the EEPROM is significantly faster than the SPI algorithm

-

The JTAG algorithm uses the same ‘JTAG Port’ as the Atmel JTAG-ICE Debugger.

-

In JTAG mode is it possible to change the ‘Clock Selection Fuses’ to any value and still program the chip. (with the exception of the ‘JTAGEN’ Fuse)

-

It is possible to daisy-chain multiple JTAG devices on the JTAG bus in a so-called ‘JTAG Chain’ and then select to program a particular device in the chain. This functionality is now supported by Equinox programmers running firmware 3.07 and above.

|

|

Portable / Field Production ISP Programmers |

|

|

Click the programmer picture for more information about the selected programmer

|

|

Production ISP Programmers |

|

|

Click on the picture of a programmer to view the full programmer description page.

|

|

JTAG connections (Single JTAG Device) |

|

|

|

- Supports high-speed JTAG programming of a single Atmel AVR microcontroller

-

Uses only 4 x JTAG pins + control of the AVR RESET pin

-

Uses the same JTAG port pins as used by the Atmel JTAG ICE debugger

|

|

JTAG Chain Programming Support |

|

|

|

- Supports programming of Atmel AVR microcontrollers which are part of a 'JTAG Chain'

-

An individual 'Programming Project' is used to program a specific 'JTAG Device' in the 'JTAG Chain'

-

The algorithm supports 'JTAG Chain' programming of both legacy AVR devices eg. ATmega16 and newer AVR devices eg. ATmega2560 with the devices placed in any order in the JTAG Chain

-

High-speed 'JTAG Chain' programming possible due to optimised algorithms

-

Supports JTAG Chain validation (checks the integrity of the JTAG Chain)

-

Supports checking of the 'JTAG ID' of any other non-AVR JTAG device eg. CPLD in the chain

|

|

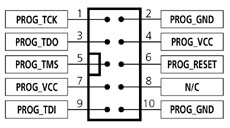

ISP Header Pin-out |

|

|

|

- Equinox programmers feature the same 10-way IDC connector as the Atmel JTAG ICE debugger

-

The same JTAG interface can therefore be used for both debugging during the "development phase" and "In-System Programming" during the "production phase"

|

| |